Analog-till-digital-omvandlare - syfte, klassificering och funktionsprincip

En elektronisk enhet som kallas en analog-till-digital-omvandlare (ADC) används för att konvertera en analog signal till en digital signal (i en läsbar binär kodtypsekvens). I processen att konvertera en analog signal till digital implementeras följande: sampling, kvantisering och kodning.

Sampling förstås som att ta sampel från en tidskontinuerlig analog signal av individuella (diskreta) värden som faller vid tidpunkter associerade med vissa intervall och varaktigheter för klocksignaler som följer varandra.

Kvantisering innebär avrundning av värdet på en analog signal vald under samplingen till närmaste kvantiseringsnivå, och kvantiseringsnivåerna har sina egna sekvensnummer, och dessa nivåer skiljer sig från varandra med ett fast deltavärde, vilket inte är något annat än kvantiseringssteg.

Strängt taget är sampling processen att representera en kontinuerlig funktion som en serie diskreta värden, och kvantisering är uppdelningen av en signal (värden) i nivåer. När det gäller kodning förstås här kodning som en jämförelse av de element som erhålls som ett resultat av kvantisering med en förutbestämd kombination av koder.

Det finns många metoder för att omvandla spänning till kod. Dessutom har var och en av metoderna individuella egenskaper: noggrannhet, hastighet, komplexitet. Beroende på typen av konverteringsmetod klassificeras ADC i tre

-

parallellt

-

konsekvent,

-

seriell-parallell.

För varje metod fortsätter processen att transformera en signal över tiden på sitt eget sätt, därav namnet. Skillnaderna ligger i hur kvantisering och kodning utförs: en seriell, parallell eller seriell-parallell procedur för att approximera ett digitalt resultat till den konverterade signalen.

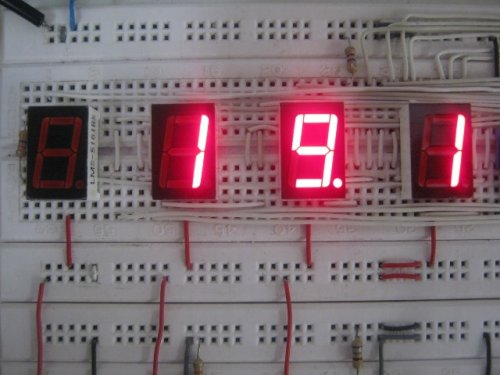

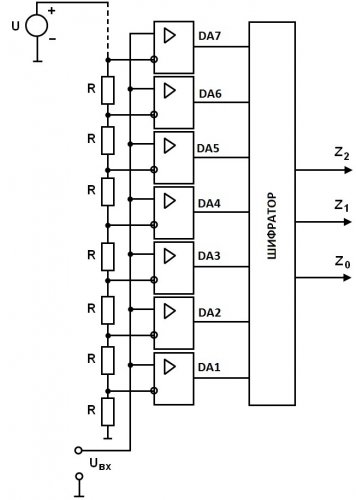

Diagrammet för en parallell analog-till-digital-omvandlare visas i figuren. Parallella ADC:er är de snabbaste analog-till-digital-omvandlarna.

Antalet elektroniska jämförelseenheter (det totala antalet DA-komparatorer) motsvarar kapaciteten hos ADC:n: tre komparatorer räcker för två bitar, sju för tre, 15 för fyra, etc. Motståndsspänningsdelaren är utformad för att ställa in ett intervall av konstanta referensspänningar.

Ingångsspänningen (värdet på denna inspänning mäts här) appliceras samtidigt på ingångarna på alla komparatorer och jämförs med alla referensspänningar för de som denna resistiva delare tillåter att erhålla.

De komparatorer vars icke-inverterande ingångar matas med en spänning som är större än referensen (tillämpas av delaren på den inverterande ingången) kommer att ge en logisk etta vid utgången, resten (där inspänningen är mindre än referensen eller lika med noll) kommer att ge noll.

Sedan ansluts en kodare, dess uppgift är att omvandla en kombination av ettor och nollor till en standard, adekvat förstådd binär kod.

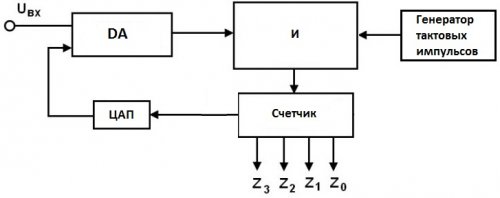

ADC-kretsar för seriell omvandling är mindre snabba än parallella omvandlarkretsar, men de har en enklare elementär design.Den använder en komparator, OCH-logik, en klocka, en räknare och en digital-till-analog-omvandlare.

Figuren visar ett diagram över en sådan ADC. Till exempel, medan den uppmätta spänningen som appliceras på ingången till komparatorkretsen är högre än rampsignalen för den andra ingången (referens), räknar räknaren klockgeneratorns pulser. Det visar sig att den uppmätta spänningen är proportionell mot antalet räknade pulser.

Det finns också serieparallella ADC:er, där processen att omvandla en analog signal till en digital signal separeras i rymden, så det visar sig att den maximala avvägningshastigheten uppnås med minimal komplexitet.